tuotteet Luokka

- FM-lähetin

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV lähetin

- 0-50w 50-1kw 2kw-10kw

- FM-antenni

- TV-antenni

- antenni Tarvikkeet

- Kaapeli liitin Virta Splitter dummy Load

- RF Transistor

- Virtalähde

- Audio Kalusto

- DTV Front End Equipment

- Link System

- STL-järjestelmän Mikroaaltouuni Link järjestelmä

- FM-radio

- Voimamittari

- Muut tuotteet

- Erityinen koronavirukselle

Tags

Fmuser Sites

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> albania

- ar.fmuser.net -> arabia

- hy.fmuser.net -> Armenian

- az.fmuser.net -> azerbaidžanilainen

- eu.fmuser.net -> baski

- be.fmuser.net -> valkovenäläinen

- bg.fmuser.net -> Bulgaria

- ca.fmuser.net -> katalaani

- zh-CN.fmuser.net -> kiina (yksinkertaistettu)

- zh-TW.fmuser.net -> Kiina (perinteinen)

- hr.fmuser.net -> kroatia

- cs.fmuser.net -> tšekki

- da.fmuser.net -> tanska

- nl.fmuser.net -> Dutch

- et.fmuser.net -> viro

- tl.fmuser.net -> filippiiniläinen

- fi.fmuser.net -> suomi

- fr.fmuser.net -> French

- gl.fmuser.net -> galicialainen

- ka.fmuser.net -> Georgian

- de.fmuser.net -> saksa

- el.fmuser.net -> Greek

- ht.fmuser.net -> Haitin kreoli

- iw.fmuser.net -> heprea

- hi.fmuser.net -> Hindi

- hu.fmuser.net -> Unkari

- is.fmuser.net -> islanti

- id.fmuser.net -> indonesia

- ga.fmuser.net -> irlantilainen

- it.fmuser.net -> Italian

- ja.fmuser.net -> japani

- ko.fmuser.net -> korea

- lv.fmuser.net -> latvia

- lt.fmuser.net -> Liettua

- mk.fmuser.net -> makedonia

- ms.fmuser.net -> malaiji

- mt.fmuser.net -> maltalainen

- no.fmuser.net -> Norja

- fa.fmuser.net -> persia

- pl.fmuser.net -> puola

- pt.fmuser.net -> portugali

- ro.fmuser.net -> Romania

- ru.fmuser.net -> venäjä

- sr.fmuser.net -> serbia

- sk.fmuser.net -> slovakki

- sl.fmuser.net -> Slovenian

- es.fmuser.net -> espanja

- sw.fmuser.net -> swahili

- sv.fmuser.net -> ruotsi

- th.fmuser.net -> Thai

- tr.fmuser.net -> turkki

- uk.fmuser.net -> ukraina

- ur.fmuser.net -> urdu

- vi.fmuser.net -> Vietnam

- cy.fmuser.net -> kymri

- yi.fmuser.net -> Jiddiš

Mikä on puolijakaja: Työskentely ja sen sovellukset, K-MAP, piiri NAND-portin avulla

Date:2021/10/18 21:55:58 Hits:

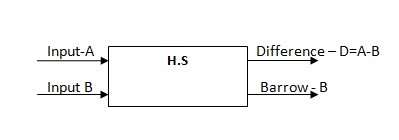

Tietojen, kuten valon tai äänen, käsittelemiseksi pisteestä toiseen voimme käyttää analogisia piirejä antamalla oikeat tulot analogisten signaalien muodossa. Tässä prosessissa analogisten sisääntulosignaalien on mahdollista saada kohinaa, ja tämä voi johtaa lähtösignaalin häviämiseen, mikä tarkoittaa sitä, että mitä tahansa tuloa, jota käsittelemme tulotasolla, ei ole sama kuin lähtövaihe. Näiden digitaalipiirien voittamiseksi toteutetaan. Digitaalipiiri voidaan suunnitella logiikkaporteilla. Logiikkaportit ovat elektroninen piiri, joka suorittaa loogisia toimintoja niiden tulojen perusteella ja antaa lähtöön vain yhden bitin, joko matalan (logiikka 0 = nollajännite) tai korkean (looginen 1 = korkea jännite). Yhdistelmäpiirit voidaan suunnitella useammalla kuin yhdellä logiikkaportilla. Nämä piirit ovat nopeita ja ajasta riippumattomia, ei palautetta tulon ja lähdön välillä. Yhdistelmäpiirit ovat hyödyllisiä aritmeettisissa ja Boolen operaatioissa. Parhaita esimerkkejä yhdistelmäpiireistä ovat puolisumma, täysi summaaja, puolivähennys, täysi vähennyslaite, multiplekserit, demultiplekserit, kooderi ja dekooderi. käytetään vähentämään kaksi bittiä tulosta. Tässä vähennyslaskurin ulostulo on puhtaasti riippuvainen nykyisistä panoksista eikä se ole riippuvainen aiemmista vaiheista. Puoli-vähennyslaskutulokset ovat ero ja kori. Se on samanlainen kuin nivelen vähennys, jossa jos vähennys on suurempi kuin minuend, menisimme lainaan B = 1 tai muuten laina pysyisi nollana B = 0. Ymmärtääksesi sen paremmin, siirry alla olevaan totuustaulukkoon.  puoli-vähennyslasku-lohkokaavioTotuuden taulukkoPuolivähennyslaskurin totuustaulukko näyttää lähtöarvot syöttövaiheissa käytettävien tulojen mukaan. Totuustaulukko on jaettu kahteen osaan. Digitaalipiirien tulo 0 ja tulo 1 ilmaisevat logiikan alhaisen ja loogisen korkean. Kokoonpanon mukaan logiikka matala tarkoittaa nollajännitettä, looginen korkea tarkoittaa korkeaa jännitettä (kuten 5V, 7V, 12V jne.). Tulot Lähdöt Tulo -AIsyöttö -BDifference -DBarrow -B 000010 1001111100 Totuustaulukon selitys Kun tulot A ja B ovat nolla, puolivähennyslaitteiden D ja B lähdöt ovat myös nolla. Kun tulo A on korkea ja B on nolla, ero on suuri eli 1 ja Barrow on nolla Kun tulo A on nolla ja tulo B on korkea, D: n ja B: n lähdöt ovat korkeat vastaavilla. Etsi eroa (D) ja Barrow (B) varten. Tästä lausunnosta D = AB '+A'B = A⊕B. D-yhtälön mukaan se merkitsee Ex- tai porttia. Tästä lähtien Barrow B: n yhtälö on, B = A'BB = A'B Yllä olevista eroista ja kynsien yhtälöistä voimme suunnitella puolivähennyspiirikaavion käyttämällä K -MapK -MapKarnaugh -kartta yksinkertaistaa Boolen algebran lauseketta puolen vähennyspiirin osalta. Tämä on virallinen menetelmä Boolen algebran yhtälön löytämiseksi mille tahansa piirille. Ratkaistaan Boolen lausekkeet puolivähennyspiirille K-kartan avulla.

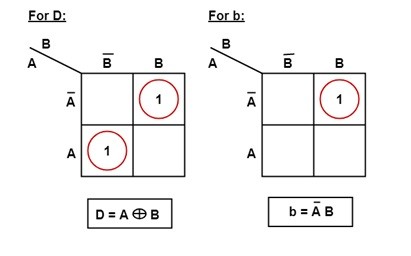

puoli-vähennyslasku-lohkokaavioTotuuden taulukkoPuolivähennyslaskurin totuustaulukko näyttää lähtöarvot syöttövaiheissa käytettävien tulojen mukaan. Totuustaulukko on jaettu kahteen osaan. Digitaalipiirien tulo 0 ja tulo 1 ilmaisevat logiikan alhaisen ja loogisen korkean. Kokoonpanon mukaan logiikka matala tarkoittaa nollajännitettä, looginen korkea tarkoittaa korkeaa jännitettä (kuten 5V, 7V, 12V jne.). Tulot Lähdöt Tulo -AIsyöttö -BDifference -DBarrow -B 000010 1001111100 Totuustaulukon selitys Kun tulot A ja B ovat nolla, puolivähennyslaitteiden D ja B lähdöt ovat myös nolla. Kun tulo A on korkea ja B on nolla, ero on suuri eli 1 ja Barrow on nolla Kun tulo A on nolla ja tulo B on korkea, D: n ja B: n lähdöt ovat korkeat vastaavilla. Etsi eroa (D) ja Barrow (B) varten. Tästä lausunnosta D = AB '+A'B = A⊕B. D-yhtälön mukaan se merkitsee Ex- tai porttia. Tästä lähtien Barrow B: n yhtälö on, B = A'BB = A'B Yllä olevista eroista ja kynsien yhtälöistä voimme suunnitella puolivähennyspiirikaavion käyttämällä K -MapK -MapKarnaugh -kartta yksinkertaistaa Boolen algebran lauseketta puolen vähennyspiirin osalta. Tämä on virallinen menetelmä Boolen algebran yhtälön löytämiseksi mille tahansa piirille. Ratkaistaan Boolen lausekkeet puolivähennyspiirille K-kartan avulla. K-kartta eroille (D) ja Barrow (B) K-kartan mukaan ensimmäinen implisiittinen on A'B ja toinen implisiittinen on AB '. = A'B+AB'Sitten D = A⊕B. Tämä yhtälö osoittaa yksinkertaisesti Ex-OR-portin. Jotta voimme löytää yksinkertaistetun Boolen lausekkeen Barrow B: lle, meidän on noudatettava samaa prosessia, jota seurasimme Difference D: lle. Siksi B = A'B. NOR -portteja kutsutaan yleisportteiksi. Tässä NAND -porttia kutsutaan yleisportiksi, koska voimme suunnitella minkä tahansa tyyppisen digitaalisen piirin käyttämällä NAND -porttien n -numeroyhdistelmiä. Tämän erikoisuuden vuoksi NAND -porttia kutsutaan yleisportiksi. Suunnittelemme nyt puoli-vähennyspiirin käyttämällä NAND-portteja.

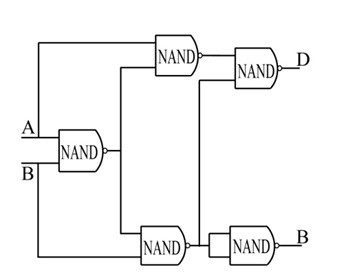

K-kartta eroille (D) ja Barrow (B) K-kartan mukaan ensimmäinen implisiittinen on A'B ja toinen implisiittinen on AB '. = A'B+AB'Sitten D = A⊕B. Tämä yhtälö osoittaa yksinkertaisesti Ex-OR-portin. Jotta voimme löytää yksinkertaistetun Boolen lausekkeen Barrow B: lle, meidän on noudatettava samaa prosessia, jota seurasimme Difference D: lle. Siksi B = A'B. NOR -portteja kutsutaan yleisportteiksi. Tässä NAND -porttia kutsutaan yleisportiksi, koska voimme suunnitella minkä tahansa tyyppisen digitaalisen piirin käyttämällä NAND -porttien n -numeroyhdistelmiä. Tämän erikoisuuden vuoksi NAND -porttia kutsutaan yleisportiksi. Suunnittelemme nyt puoli-vähennyspiirin käyttämällä NAND-portteja. Voimme suunnitella puolivähennyspiirin, jossa on viisi NAND-porttia. Tarkastellaan A: ta ja B: tä NAND-portin ensimmäisen vaiheen tuloina, ja sen lähtö kytketään jälleen yhdeksi tuloksi toiseen NAND-porttiin sekä kolmas NAND -portti. Tulojen mukaan se antaa ulostulon, ja NAND -porttien viimeisessä vaiheessa erotusteho D ja korin lähtö B ovat niiden ulostulossa. ⊕B ja Barrow B -yhtälö B = A'B.Kun käytetään eri NAND-porttien yhdistelmää puolivähennyslaskurin rakentamiseen, lopulliset ero- ja kynnysyhtälöt ovat D = A⊕B ja B = A'B. Half Subtractor Näitä vähentäjiä on useita sovelluksia. Käytännössä niitä on helppo analysoida. Jotkut niistä on lueteltu seuraavasti: Jos haluat vähentää sarakkeissa pienimmässä paikassa olevat numerot, nämä vähennyslaskut ovat edullisia. Tarvittavan toiminnan perusteella puolivähennyslaite pystyy lisäämään tai vähentämään operaattoreiden määrää. Vahvistimessa käytetään puolivähennyksiä. Kun lähetetään audiosignaaleja, niitä käytetään vääristymien välttämiseen. Puolet vähennyspiiri. Reaaliaikaisissa olosuhteissa useiden bittimäärien vähentämistä ei voida tehdä käyttämällä puolivähennyksiä. Tämä haittapuoli voidaan voittaa käyttämällä täydellistä alihankkijaa.

Voimme suunnitella puolivähennyspiirin, jossa on viisi NAND-porttia. Tarkastellaan A: ta ja B: tä NAND-portin ensimmäisen vaiheen tuloina, ja sen lähtö kytketään jälleen yhdeksi tuloksi toiseen NAND-porttiin sekä kolmas NAND -portti. Tulojen mukaan se antaa ulostulon, ja NAND -porttien viimeisessä vaiheessa erotusteho D ja korin lähtö B ovat niiden ulostulossa. ⊕B ja Barrow B -yhtälö B = A'B.Kun käytetään eri NAND-porttien yhdistelmää puolivähennyslaskurin rakentamiseen, lopulliset ero- ja kynnysyhtälöt ovat D = A⊕B ja B = A'B. Half Subtractor Näitä vähentäjiä on useita sovelluksia. Käytännössä niitä on helppo analysoida. Jotkut niistä on lueteltu seuraavasti: Jos haluat vähentää sarakkeissa pienimmässä paikassa olevat numerot, nämä vähennyslaskut ovat edullisia. Tarvittavan toiminnan perusteella puolivähennyslaite pystyy lisäämään tai vähentämään operaattoreiden määrää. Vahvistimessa käytetään puolivähennyksiä. Kun lähetetään audiosignaaleja, niitä käytetään vääristymien välttämiseen. Puolet vähennyspiiri. Reaaliaikaisissa olosuhteissa useiden bittimäärien vähentämistä ei voida tehdä käyttämällä puolivähennyksiä. Tämä haittapuoli voidaan voittaa käyttämällä täydellistä alihankkijaa.

Jätä viesti

viestiluettelo

Kommentit Loading ...